一、先进封装市场规模

全球半导体产业正处于一段转折期。摩尔定律逐渐到头,成本不断上升,促使业界开始依靠IC封装来扩大在超越摩尔时代的获利。因此,得益于对更高集成度的广泛需求;摩尔定律的放缓;以及交通、5G、消费类、存储和计算、物联网(包括工业物联网)、人工智能(AI)和高性能计算(HPC)等大趋势的推动,先进封装逐步进入其最成功的时期。

数字时代的大趋势和驱动因素

数据来源:公开资料整理

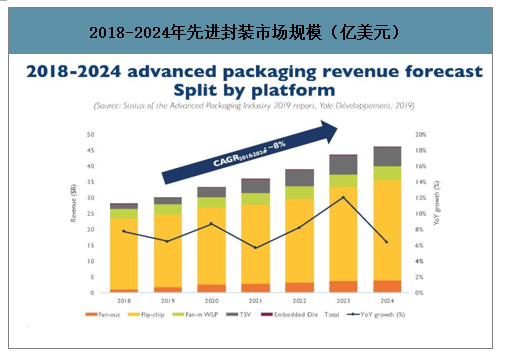

先进封装延续摩尔定律,市场规模持续增长。智研咨询发布的《2020-2026年中国电子封装行业市场专项调查及投资前景展望报告》显示:尽管2019年半导体产业将出现放缓,然而先进封装市场仍将保持增长趋势,同比增长约6%。2024年先进封装市场规模将达440亿美元,2018~2024CAGR达8%的成长,同一时期,Yole预测传统封装市场CAGR为2.4%,IC封装产业整体CAGR为

2018-2024年先进封装市场规模(亿美元)

数据来源:公开资料整理

2018年,倒装芯片(FLIP-CHIP)占先进封装市场的81%。不过,到2024年,其市场份额预计将下降至约72%。在各个先进封装平台中,3DIC堆叠和扇出型封装将以约26%的速度增长,在各个领域的应用将持续增长。没有其他哪种技术可以提供基于硅通孔(TSV)、混合键合(或两者的组合)的堆叠技术所能达到的性能和集成水平。3D存储(HBM和3DDDRDRAM)、基于2.5D中介层的芯片分割和逻辑存储器集成,推动了高端TSV市场的增长。

由人工智能/机器学习(AI/ML)、HPC和数据中心引领的高带宽存储(HBM)业务正在快速增长。扇出型封装正在更多应用(BB、PMIC、RF、APE、存储器)中得到采用,同时不断渗透到新的市场。事实上,随着不同商业模式的厂商争相进入市场,扇出型封装市场预计将呈现强劲增长。2019年~2024年期间,源自移动设备的引领,扇入型晶圆级封装(WLP)将以6.5%的复合年增长率增长。嵌入式芯片虽然市场规模较小(2018年小于2500万美元),但未来五年,凭借电信和基础设施、汽车和移动等市场需求推动,预计将以49%的复合年增长率增长。

在应用方面,2018年,移动和消费类应用占据先进封装市场总量的84%。2019年~2024年期间,该应用市场预计将以5%的复合年增长率增长,到2024年占先进封装总量的72%。而在营收方面,电信和基础设施是先进封装市场增长最快的细分领域(约28%),其市场份额将从2018年的6%增长到2024年的15%。与此同时,汽车和交运细分领域的市场份额预计将从2018年的9%增长到2024年的11%。

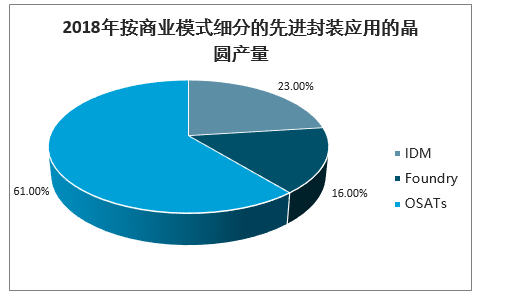

2018年按商业模式细分的先进封装应用的晶圆产量

数据来源:公开资料整理

随着智能驾驶、AIOT、数据中心及5G等市场的成熟,预计2.5D/3DTSV技术、FanOut技术、ED技术等先进封装技术的市场规模CAGR将保持高速增长,分别达26%、26%、49%。晶方科技目前主要技术集中在WLSCP、TSV、FAN-OUT等先进封装工艺、LGA/MOUDLE等芯片级封装工艺。

未来主流先进封装技术大放异彩

技术名称 | 2018-2024RevenueCAGRs | 渗透应用领域 |

2.5D/3DTSV | 26% | 手机、汽车等 |

FAN-OUT | 26% | AI/ML、HPC、数据中心、CIS、MEMS/传感器等 |

EmbeddedDie(ED) | 49% | 汽车、医疗等 |

除传统OSAT企业,近年一些IDM和Foundry也在内部开始发展封测业务以提升自身生产效率和自主服务能力。这些业务多集中在先进封装技术,使得这些厂商在封测行业持续保持先进性和核心竞争力,如台积电的SoIC(系统整合晶片封装)和WoW(16

纳米晶圆堆叠晶圆)等3DIC封装技术,预期2021年进入量产。

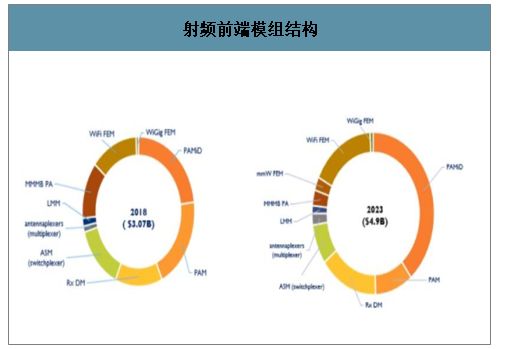

二、SiP:集成化封装及5G射频要求提升,SiP需求大增

5G对于封装需求要求提升,器件封装微小化、复杂化、集成化。5G时代采用高频的毫米波段对应更小尺寸的射频元件,其封装复杂度大幅提升,对封装过程中的连线、垫盘和通孔等结构精密度要求更高,避免妨碍到芯片上的射频功能。5G时代,由于越来越多的频段需求,在射频前端模组化趋势下,RF封装呈现集成化,SiP解决方案会得到更加广泛的应用集成化方案尺寸小、响应快、性能好,2018年占比射频元件比重超过50%。手机轻薄化不断提升,以及射频元件数量的增加,因而在有限的内部空间,射频前端呈现了集成化的趋势。集成化除了在减少尺寸之外,还具有节省客户调试时间,缩减手机研发周期和提供更好的半导体性能两大优点。未来射频前端集成化占比会越来越高,在2017年已经达到了50%,2018年则成为最主要方案。

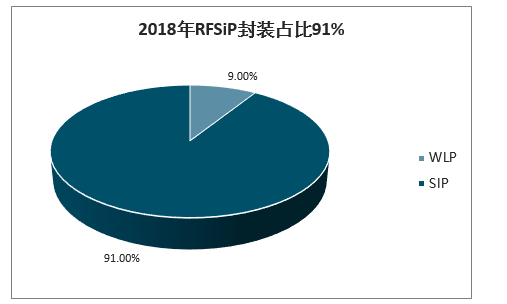

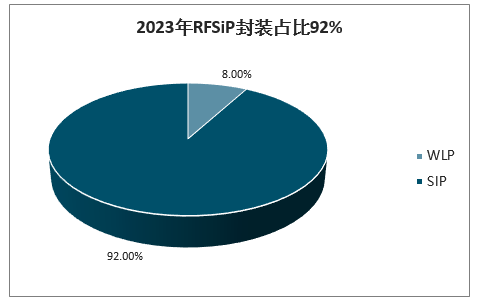

材料的多样性要求先进封装技术,SiP将脱颖而出。随着移动通讯技术的升级,射频芯片采用的工艺也越来越复杂,对PA而言最好的工艺是GaAs,对天线开关而言最好的工艺是SOI,滤波器则是采用压电材料。SOC方案难以集成这些不同材料;系统性封装SiP才能满足这些要求。因而5G时代的射频前端集成化,将采用先进封装技术。据预测,移动端RFSiP市场规模将由2018年的33亿美金增长到2023年的53亿美金。

射频前端的SiP封装将进入一个快速增长期。其中,集成PA、Filter、Swtich的PAMid增长最快,在射频前端模组中的比重从23%增长到39%。

2018年RFSiP封装占比91%

数据来源:公开资料整理

2023年RFSiP封装占比92%

数据来源:公开资料整理

射频前端模组结构

数据来源:公开资料整理

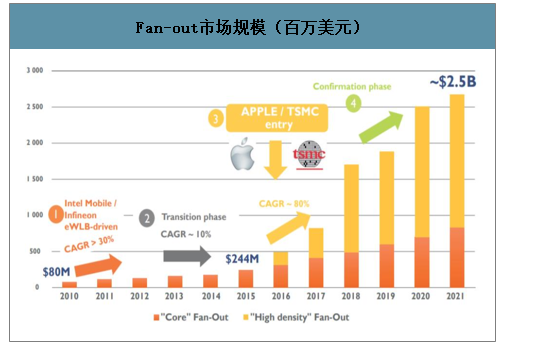

三、、FOWLP:封装技术持续升级,FOWLP保持高速增长

扇出型晶圆级封装的英文全称为Fan-OutWaferLevelPackaging,即FOWLP,是指将来自于异质制程的多颗晶粒结合到一个紧凑封装中的新方法。由于对更薄功能和增加I/O数量设备的需求,扇出式WLP受到越来越多的关注。随着FOWLP技术不断发展,从单芯片应用拓展至MCP(多芯片封装)及3DPoP(堆叠式封装)等,应用于更高I/O芯片的整合中。

FOWLP充分利用RDL做连接,实现互连密度最大化。传统的WLP封装多采用Fan-in型态,应用于低接脚(Pin)数的IC。当芯片面积缩小的同时,芯片可容纳的引脚数减少,因此变化衍生出扩散型FOWLP封装形态,实现在芯片范围外充分利用RDL做连接,以此获取更多的引脚数。在一个环氧行化合物(EMC)中嵌入每个裸片时,每个裸片间的空隙有一个额外的I/O连接点,这样I/O数会更高并且的对硅利用率也有所提高,使互连密度最大化,同时实现高带宽数据传输。

FOWLP降低封装成本,减少封装厚度。相比于扇入型封装技术,FOWLP的优势在于:减小了封装厚度、扩展能力(用于增加I/O数量)、改进的电气性能、良好的热性能以及无基板工艺。扇出WLP在结构上类似于传统的球栅阵列(BGA)封装,但是消除了昂贵的衬底工艺

FOWLP被广泛应用,市场规模保持高速增长。FOWLP封装最早在2009~2010年由Intel提出,仅用于手机基带芯片封装。一直到2015年以前,FOWLP市场较小且主要应用于基带、RF、PMU等单芯片扇出封装。2016年,台积电将InFO技术应用于iPhone的AP芯片,实现高密度扇出封装,并逐渐应用于智能手机、HPC、通讯等各种领域,市场空间在2016~2017年爆发。根据最新预测,FOWLP市场规模将在2019~2024年的复合增长为19%,2024年市场空间将达到38亿美元。日月光和台积电一样,在2016年实现FOWLP量产,安靠、矽品、力成在2017年紧接着布局。

Fan-out市场规模(百万美元)

数据来源:公开资料整理

公众号

公众号

小程序

小程序

微信咨询

微信咨询

![2026年中国白羽肉鸡行业产业链图谱、出栏量、竞争格局及未来竞争趋势分析:禾丰股份与圣农发展龙头优势明显[图]](http://img.chyxx.com/images/2022/0330/b388a599ab8b82a70e79838a8b0d600efa11727f.png?x-oss-process=style/w320)

![2026年全球及中国汽车美容行业产业链、市场规模、竞争格局及发展趋势研判:产业呈现出蓬勃发展之势,国内汽车美容市场规模将达7608亿元[图]](http://img.chyxx.com/images/2022/0330/ce25a2275c336b52d58303ed80fb7924b3fd1022.png?x-oss-process=style/w320)

![2026年中国固态电池行业产业链、出货量、投融资事件、主要企业产能、兼并重组事件、企业区域分布及竞争趋势:资本持续加码布局,产业化进程加速[图]](http://img.chyxx.com/images/2022/0330/dd2a6e2dd1963d26c8672c625ba6166e69bd4120.png?x-oss-process=style/w320)